### CprE 450/550X Distributed Systems and Middleware

### Consistency & Replication

Yong Guan

3216 Coover

Tel: (515) 294-8378

Email: guan@ee.iastate.edu

April 8, 2003

### Readings for Today's Lecture

- > References

- ➤ Chapter 6 of "Distributed Systems: Principles and Paradigms"

- |

## Introduction to Consistency & Replication Object Replication Server machine Glent machine Server machine Glent machine Organization of a distributed remote object shared by two different clients.

## Object Replication (3) | A distributed system for replication-aware distributed objects. A distributed system responsible for replica management

# Strict Consistency P1: W(x)a P2: R(x)n P2: R(x)NIL R(x)a (a) Behavior of two processes, operating on the same data item. A strictly consistent store. A store that is not strictly consistent.

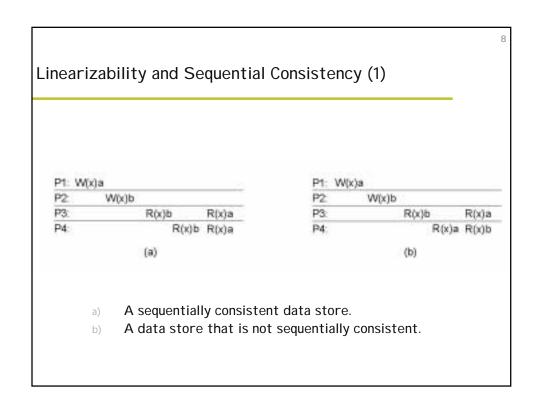

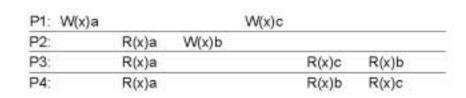

Linearizability and Sequential Consistency (2)

| Process P1     | Process P2    | Process P3    |

|----------------|---------------|---------------|

| x = 1;         | y = 1;        | z = 1;        |

| print ( y, z); | print (x, z); | print (x, y); |

Three concurrently executing processes.

Linearizability and Sequential Consistency (3)

x = 1;x = 1;print ((y, z); y = 1;z = 1;x = 1;y = 1;print (x,z); print (x, y); z = 1;print (x, z); print(y, z); print (x, z); print (x, z); z = 1;x = 1;z = 1;print (y, z); print (x, y); print (x, y); print (y, z); print (x, y); Prints: 001011 Prints: 101011 Prints: 010111 Prints: 111111 Signature: Signature: Signature: Signature: 001011 101011 110101 111111 (a) (b) (c) (d)

Four valid execution sequences for the processes of the previous slide. The vertical axis is time.

11

### Casual Consistency (1)

Necessary condition: Writes that are potentially casually related must be seen by all processes in the same order. Concurrent writes may be seen in a different order on different machines.

### Casual Consistency (2)

12

This sequence is allowed with a casually-consistent store, but not with sequentially or strictly consistent store.

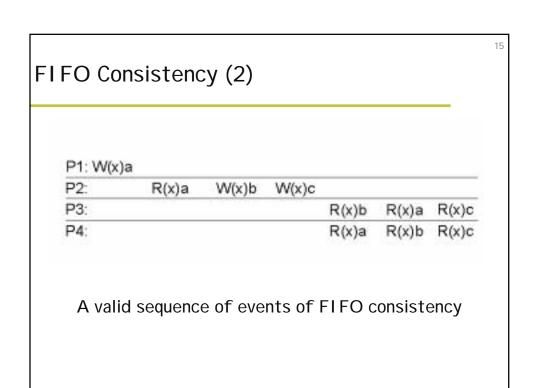

Casual Consistency (3) P1: W(x)a P2 R(x)a W(x)b P3: R(x)b R(x)a P4: R(x)a R(x)b P1: W(x)a P2: W(x)b R(x)b R(x)a P4: R(x)a R(x)b (b) A violation of a casually-consistent store. a) A correct sequence of events in a casually-consistent store. b)

### FIFO Consistency (1)

Necessary Condition:

Writes done by a sine

Writes done by a single process are seen by all other processes in the order in which they were issued, but writes from different processes may be seen in a different order by different processes.

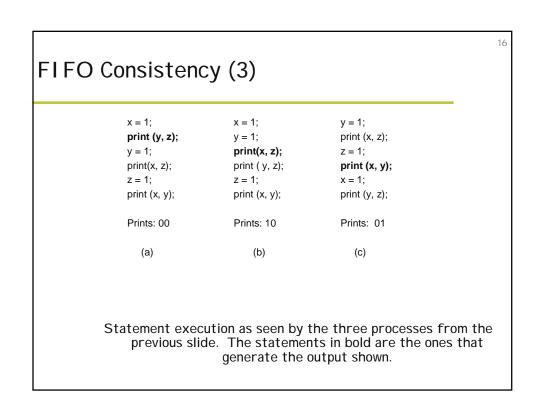

17

### FIFO Consistency (4)

| Process P1               | Process P2               |

|--------------------------|--------------------------|

| x = 1;                   | y = 1;                   |

| if $(y == 0)$ kill (P2); | if $(x == 0)$ kill (P1); |

|                          |                          |

|                          |                          |

Two concurrent processes.

18

### Weak Consistency (1)

- Properties:

- Accesses to synchronization variables associated with a data store are sequentially consistent

- No operation on a synchronization variable is allowed to be performed until all previous writes have been completed everywhere

- No read or write operation on data items are allowed to be performed until all previous operations to synchronization variables have been performed.

Weak Consistency (2)

```

int a, b, c, d, e, x, y;

/* variables */

int *p, *q;

/* pointers */

int f( int *p, int *q);

/* function prototype */

/* a stored in register */

a = x * x;

b = y * y;

/* b as well */

c = a*a*a + b*b + a*b;

/* used later */

/* used later */

d = a * a * c;

p = &a;

/* p gets address of a */

q = &b

/* q gets address of b */

e = f(p, q)

/* function call */

```

A program fragment in which some variables may be kept in registers.

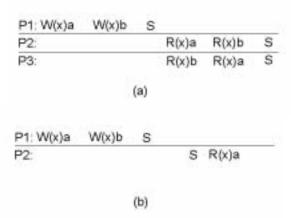

### Weak Consistency (3)

- a) A valid sequence of events for weak consistency.

- b) An invalid sequence for weak consistency.

9

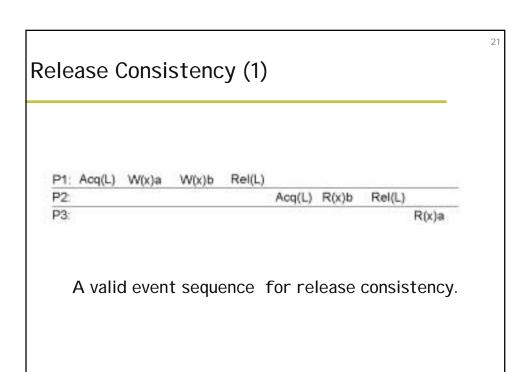

### Release Consistency (2)

- Rules:

- Before a read or write operation on shared data is performed, all previous acquires done by the process must have completed successfully.

- Before a release is allowed to be performed, all previous reads and writes by the process must have completed

- Accesses to synchronization variables are FIFO consistent (sequential consistency is not required).

### **Entry Consistency (1)**

23

- Conditions:

- An acquire access of a synchronization variable is not allowed to perform with respect to a process until all updates to the guarded shared data have been performed with respect to that process.

- Before an exclusive mode access to a synchronization variable by a process is allowed to perform with respect to that process, no other process may hold the synchronization variable, not even in nonexclusive mode.

- After an exclusive mode access to a synchronization variable has been performed, any other process's next nonexclusive mode access to that synchronization variable may not be performed until it has performed with respect to that variable's owner.

### Entry Consistency (2)

24

P1: Acq(Lx) W(x)a Acq(Ly) W(y)b Rel(Lx) Rel(Ly)

P2: Acq(Lx) R(x)a R(y)NIL

P3: Acq(Ly) R(y)b

A valid event sequence for entry consistency.

25 Summary of Consistency Models Consistency Description Absolute time ordering of all shared accesses matters. All processes must see all shared accesses in the same order. Accesses are furthermore ordered according to Linearizability a (nonunique) global timestamp Sequential All processes see all shared accesses in the same order. Accesses are not ordered in time Causal All processes see causally-related shared accesses in the same order. All processes see writes from each other in the order they were used. Writes from different processes may not FIFO always be seen in that order Consistency Weak Shared data can be counted on to be consistent only after a synchronization is done Release Shared data are made consistent when a critical region is exited Entry Shared data pertaining to a critical region are made consistent when a critical region is entered. Consistency models not using synchronization operations. a)

Models with synchronization operations.